上海芯炽SC1254 与ADI AD9253 差别

2024-2-24 15:43:11 点击:

一. ADC 采样输出延时

AD9253 输出延时为 17 个时钟延时。

SC1254 的 ADC 一旦开始上电工作后第一个采样的点到 AD 输出的延迟是固定的是采样时钟的 19 个时钟周期,后续即根据时钟速度一直输出后续所转化的数据,只有第一次上电建立的时候会有一个固定延时,此延时如需确定,需要将寄存器 0x3D 地址配置为 0x20 延迟 10ms 后将 0x3D 地址再配置为 0x00。

二. ADC 四通道输出对齐

SC1254 如需通道对齐则需要将寄存器 0x08 地址配置为 0x03 延迟 10ms 后将 0x08 地址再配置为 0x00 将数字FIFO 复位即可对齐四通道数据。

三. ADC VREF 默认输出

SC1254 的 VREF 引脚默认不输出,如要输出需要进行配置:将 30 地址配置为 F6。

四. ADC 时钟输入悬空时

SC1254 时钟输入悬空时功耗较大。属于正常现象。

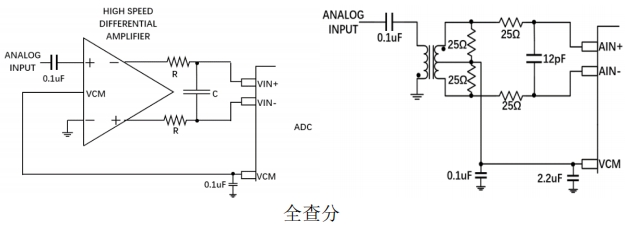

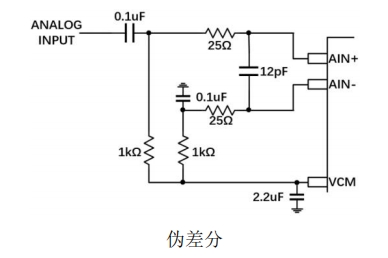

五. 输入结构区别

AD9253 的输入支持全查分与伪差分,伪差分有效位 10 位左右。

SC1254 输入信号的幅度调整到差分模拟输入范围 2Vpp 以内,可以采用差分运算放大器或巴伦作为模拟输入的前端,芯片的 VCM 输出要接入运放或巴伦的共模电压输入。运放或巴伦选择适合输入带宽即可,差分输入的 RC网络,可以参考数据手册或根据 1/(2πRC)计算。伪差分结构有效位会降低到 7 位以下。且差分输入共模要保持在 0.95V 附近。

全查分伪差分

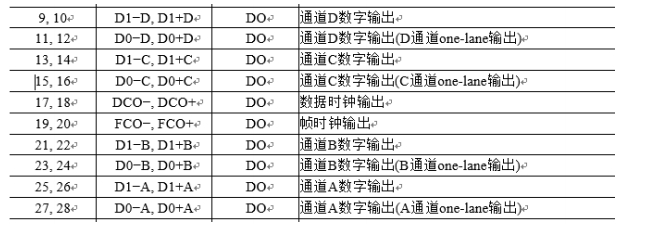

六. One-lane 输出通道有区别

AD9253 one-lane 输出如下:

SC1254 one-lane 输出如下:

且 one-lane 输出需要配置:0x3F 配置为 0x04;0x32 配置为 0x00;0x21 配置为 0x40

七. 寄存器区别(具体寄存器地址请以手册为准)

(1) 调节 DCO 与 DATA delay 寄存器区别:

AD9253 可进行 DCO 输出相位以及输入时钟的相位调节,可通过 0x16 地址的 bit[3:0]配置 DCO 的输出相位,0x16 地址的的 bit[6:4]配置输入时钟的相位。

SC1254 调节 DCO、FCO 与 DATA 延时,DCO 延时可通过 0x33 地址的 bit[4:2]选择相对应的档位进行调节;FCO 延时可通过 0x17 地址的 bit[7:5]选择相对应的档位进行调节,另外可以通过 0x33 地址的 bit0 对 DCO 输出进行反相,通过 0x33 地址的 bit1 对 FCO 输出进行反相(FCO 的输出模式可以通过 0x35 地址的 bit[3:0]进行调节)。DATA 延时配置地址在 0x42 可通过 bit[2:0]调节 D0 输出延时;bit[5:3]调节 D1 输出延时。

(2) 时钟分频寄存器区别:

AD9253 时钟分频器调节 0x0B 地址的 bit[2:0]的 000-111,分别对应 1-8 分频。

SC1254 时钟分频器调节 0x0B 地址的 bit[3:0]的 0000-1000,分别对应 1-8 分频(即 0000 与 0001 均代表 1 分频)。

(3) 测试模式下两种模式输出有所区别

AD9253 在+Full-scale short 16bit 模式的数字测试字输出为 1111 1111 1111 1100;在 checkboard 16bit 模式的数字测试字输出为 1010 1010 1010 1000。

SC1254 在+Full-scale short 16bit 模式的数字测试字输出为 1111 1111 1111 1111;在 checkboard 16bit 模式的数字测试字输出为 1010 1010 1010 1010。

(4) 输出调整区别:

AD9253 输出调整在 0x15 地址:bit[5:4]调节 LVDS 输出端接电阻阻值,以及 bit0 调节输出驱动能力。

SC1254 输出调整在 0x34 与 0x41 地址,0x34 地址可以调节 DCO 与 FCO LVDS 输出端接电阻阻值,0x41 地址可以调节 D0 与 D1 LVDS 输出端接电阻阻值。

(5) 未有寄存器

AD9253 的 0xFF 地址的 bit0 为传输数据使能;0x09 地址 bit0 为时钟占空比稳定器使能;0x0C 地址 bit2 为斩波功能使能;0x18 地址 bit[2:0]内部基准电压调节;0x101 地址 bit0 为 SDIO 关断。

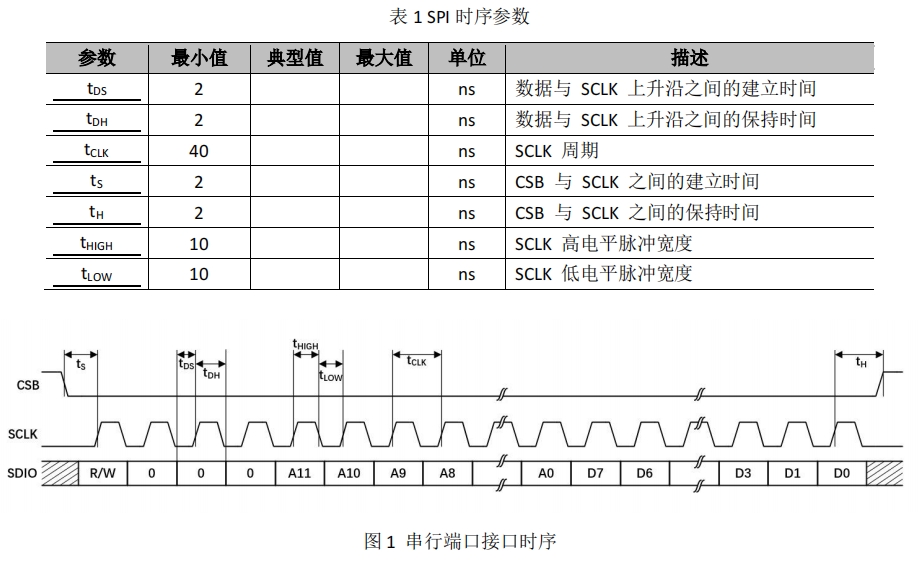

SC1254 未有 AD9253 中该功能的寄存器。表 1 SPI 时序参数

图 1 串行端口接口时序

SPI 时序为 CPOL=0,CPHA=0;

最高位为读写使能位 1:读;0:写;

寄存器地址为 12 位 A11-A0,A11 为 MSB,A0 为 LSB;

寄存器地址对应的数据为 D7-D0,D7 为 MSB,D0 为 LSB;

- 上一篇:上海芯炽SC1249 14 位 3GSPS JESD204B 2024/2/24

- 下一篇:SC1464 16通道集成16位1 MSPS双极性输入、双路 2024/2/5